## Part A

1) As a state machine, the D FF has

1 input called D + 1 clock input

1 output called Q D a

The question specifies that this state machine must be built using J-K FF.

Because the D FF has only two states (which can be considered directly as its output), we will take the output of the J-K FF to be the output of our state machine.

CLK J Q Q

The CLK signal is connected to the clock input of the J-K FF. (This is always the case for synchronous logic design. The clock inputs of all FFs receive the same CLK signal)

We can draw the state diagram from the rule that "a will follow D" on the next rising edge of the clock signal.

The number of The

in here indicate the current state of the J-K FF

The number on the arrow indicate the value of D.

Number 1 on the arrow means D=1.

Number 1 inside means current Q = 1.

For D FF, we know that the next Q will follow D.

So, the next Q = 1. This is represented by the arrow going back into state value 1.

From the state (transition) diagram, we can read off the values for the next-state table.

|       |           | We may use the notation                     |

|-------|-----------|---------------------------------------------|

| Input | s ta      |                                             |

| D     | Current Q | (Next Q' tre "next Q".                      |

| 0 0 1 | 0         | This should read "the next value of Q after |

| 1     |           | 1 tre next clock rising edge."              |

These two columns contain all possible combination of D and "current Q".

(Alternatively, we can copy the value from the D column into the "next Q column because Q will follow D.)

We use the value of

D and the current value of Q to find the next value of Q.

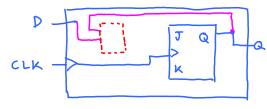

In the circuit below, this is represented by the a being fed back and the D input being connected into the red box shown in the figure here.

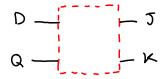

The red box above

- 1) use the current value of D and Q,

- 2) calculate what should be the next value of Q according to the next-state table above,

- 3) control the J,K injuts of the FF so that appropriate next value of Q shows up on the output of the J-K FF.

So, the inputs of the red box are D and Q the outputs of the red box are Jandk.

Enal Ha and chata Lable a con that

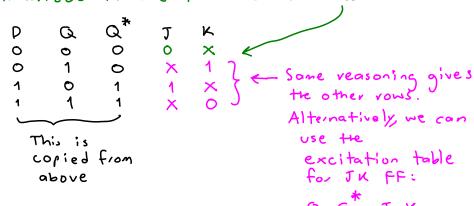

From the next-state table, we see that if D=0 and Q=0, we want Q\*=0.

Because Q\* is the output of the JK FF, we need T=0 and K=0 (hold mode) for the Q\* to stay at the same value as Q.

Alternatively, we can make J=0 and K=1, in which case, Q\* is forced to be 0 because the FF is in RESET mode. In conclusion, if D=0 and Q=0, we want J=0 and K=X; that is both K=0 adK=1 will work. This idea is summarized in the 1st row of the table below

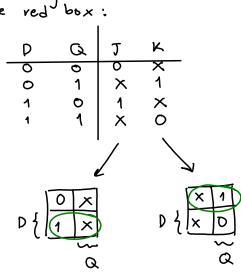

At this point, we have the following truth table for the red box:

K-maps show that J = D and  $K = \overline{D}$

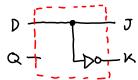

Therefore, the red box is simply:

Note the Q (the current state) is not used.

Finally, we put this red box into the circuit

that we had drawn before:

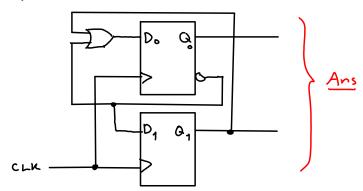

2 In this problem, there are three states, so two FFs should be enough to represent all three states.

(n FFs con represent 2" states)

We will take the output of the counter to be the same as the output of the FF.

(Q,Q,)

Next, we construct the the next-state table from the state transition diagram:

| Q* | Q* | ← Again                             | tre   | *     | means                                      |

|----|----|-------------------------------------|-------|-------|--------------------------------------------|

|    | -1 | - 1.021.                            |       |       |                                            |

| 0  | 0  |                                     |       |       |                                            |

| ×  | X  |                                     |       |       |                                            |

| 0  | 1  |                                     |       |       |                                            |

|    |    | * G, G,<br>1 1<br>0 0<br>X X<br>0 1 | . 9 1 | . 9 1 | * * Again the *  1 1  next.  0 0  X X  0 1 |

The question specifies that we must use D FFs. In general, for D FF, Q\* = D. So, from the obove table we know that

$$D_1 = Q_1^*$$

and  $D_0 = Q_0^*$ .

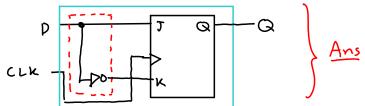

Hence, we have the following truth table for the circuit that compute D1, Do from Q1, Q0:

K-maps show that  $D_1 = \overline{Q}_0$

Hence, our final answer is

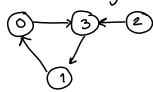

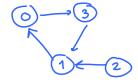

3) If I solve problem 2) correctly the only unknown transition now is the transition from state "2" which is left as don't care in the "next-state" table in problem 2.

For state "2",  $Q_1 = 1$  and  $Q_0 = 0$ .

Because  $D_1 = \overline{Q}_0$  and  $D_0 = \overline{Q}_0 + Q_1$

we have  $D_1 = 1$  and  $D_0 = 1$ . For D FF, "Q follows D."

Hence,  $Q_1^* = 1$  and  $Q_0^* = 1$ , which is state "3"

So, we know that "2" will go to "3".

The complete state diagram is

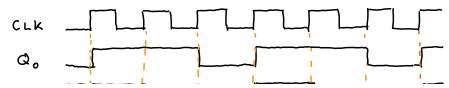

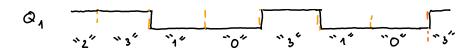

4) If we assume that the counter start from state "2", then, from the state diagram that we derived in problem 3) we know that the counting sequence is

sequence;

3-1-0-3-1-0-int the state diagram?

This is the

The waveform is drawn below:

5) The solution for this problem starts the same way as problem 2) upto the point where we have the next-state table:

| 0,00 | 0, 0° |

|------|-------|

| 0 0  | 1 1   |

| 0 1  | 0 0   |

| 1 0  | × ×   |

| 1 1  | 0 1   |

The difference between this problem and problem (2) is that we are now required to use JK FFs instead of D FFs.

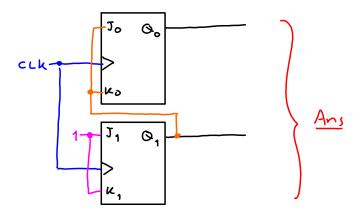

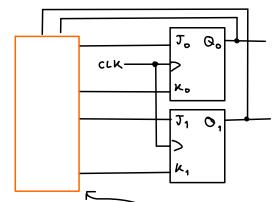

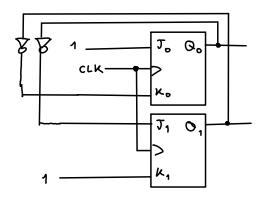

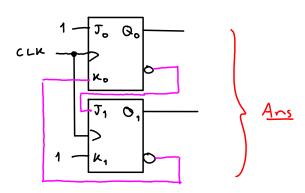

so, the circuit would be:

our job is to determine the combinational circuit inside this box). Again, this box take the current QQ value and then compute appropriate Jik, Jo, K, value so that the next Q's (Q†Q\*) are correct.

We will use the excitation table to help us determine the input to the JK FFs.

| 0,00 | 0 * Q* | JK           | Joko  |

|------|--------|--------------|-------|

| 0    | 7 1    | $(1 \times)$ | 1 X   |

| 0 1  | 00     | Ox           | X 1   |

| 1 0  | ××     | /(x x        | (X,X) |

| 1 1  | 01     | X 1          | ΧO    |

| •    |        |              | •     |

To get this we first look at Q, and Q, for this row.

These are all X because we don't care about where state "2"

we notice that  $O_1 = 0$  and  $O_1^* = 1$ From the excitation table we must have  $J_1 = 1$ ,  $K_1 = X$ .

| Excita    | ation to | .ble   |

|-----------|----------|--------|

|           | Eo,      | JK FF3 |

| Q Q*      | JK       |        |

| 00        | 0 X      | _ \    |

| 0 1       | 1 X      |        |

| 1 1       | X 1      |        |

|           |          |        |

| this      |          |        |

| ond Ot=1. |          |        |

will go next.

Note that

all index are the same.

That is, we are working with the FF labeled "1".

We can then copy down the truth table for the orange box above:

K-maps give J1=Q0, K1=1, J0=1, K0=Q1

If your JK FFs has the Q output, then we can eliminate the two NOT gates as followed:

Note that when  $Q_1 = 1$  and  $Q_0 = 0$  (we are at state "2")

Hence Q = 0 and Q = 1

So, state 2" will go to "1" on the next clock julse.

Tre complete state diagram is shown below:

6) The purpose of the count mable (CTEN) is to allow us to stop (hold) the counting.

For every clock pulse, we check the value of CTEN.

When CTEN=1, the counting goes according to what we had in problem (2).

When CTEN = 0, the counting STOP and we sit at the same state.

The new state diagram become

In this case we want to modify circuit in problem 2 so that it take into account the CTEN signal.

Back in problem 2 we have

Because in problem (2), the counting always continue, the above equations should hold for us in the case that CTEN=1.

(In other words, if CTEN is always "1", then we would observe exactly the same output as in problem (2).)

When CTEN = 0, we want to hold the value.

01 = Q, and 00 = 00.

To do this, because Q = D for DFF, we connect

$$D_1 = Q_1$$

and  $D_0 = Q_0$ .

Hence we have two cases:

when CTEN=1, D1=Q0 and D0=Q0+0, when CTEN=0, D1=Q1 and D0=Q0

These can be combined into

D1 = CTEN Q + CTEN Q1

I simplify it one more step.

Do = CTEN · (Qo+Q1) + CTEN · Q = CTEN + Oo + CTEN · O1

(You can check them by letting CTEN=0 or by letting CTEN=1)

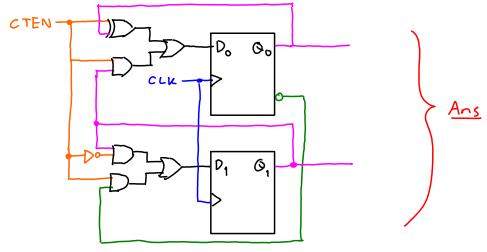

The modified circuit become

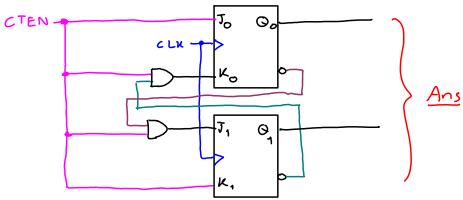

7) This is the same as problem 6 except that we now have to deal with JK FF.

It turns out that this case is even easier.

When CTEN = 1, we keep the same connection.

When CTEN =0, we want to hold and therefore all T, K values must be 0.

Hence, the combined expression is

$$J_0 = CTEN \cdot 1 + CTEN \cdot 0 = CTEN$$

$K_0 = CTEN \cdot Q_1 + CTEN \cdot 0 = CTEN \cdot Q_1$

$J_1 = CTEN \cdot Q_0 + CTEN \cdot 0 = CTEN \cdot Q_0$

$K_1 = CTEN \cdot 1 + CTEN \cdot 0 = CTEN$

Part B

18 I will only show the necessary steps in this problem.

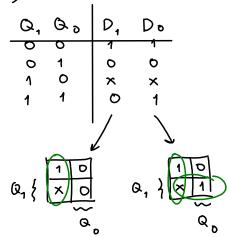

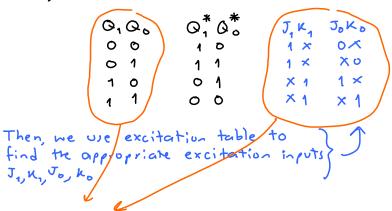

First, we construct the next-state table:

This becomes the truth table for the circuit that produces J, K, Jo, Ko.

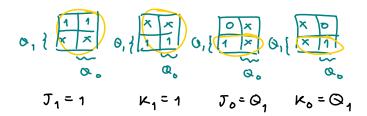

The corresponding K-maps are

Hence the circuit for the counter is